Resumen ejecutivo

Google TPU v8 marca un cambio práctico en el diseño de aceleradores de IA: el entrenamiento y la inferencia ya no se tratan como el mismo problema de hardware. La familia v8 separa los sistemas de entrenamiento de alto rendimiento de los sistemas optimizados para inferencia, de modo que cada uno pueda ajustar el ancho de banda de la memoria, el comportamiento de interconexión, la sincronización, el diseño térmico y la estructura de costos en torno a su carga de trabajo real.

Para los equipos de OEM, EMS, infraestructura de nube y abastecimiento, el mensaje es claro: la adquisición de computación de IA está pasando de la comparación chip por chip a la evaluación de la arquitectura a nivel de sistema.

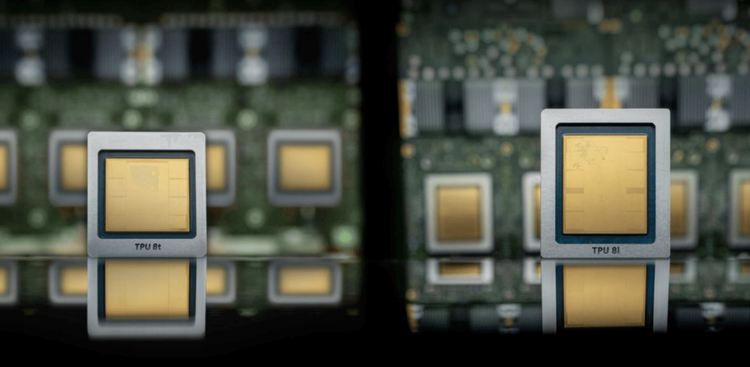

Vision general de la arquitectura

La generación TPU v8 se analiza comúnmente a través de dos direcciones complementarias. TPU 8t está dirigido a la capacitación a gran escala, donde la computación densa, el ancho de banda de la memoria y la comunicación a escala de clúster determinan el tiempo y la utilización de la capacitación. TPU 8i está dirigido a la inferencia, el muestreo y el servicio de cargas de trabajo, donde la latencia, la flexibilidad de los lotes, el enrutamiento de modelos y la eficiencia energética a menudo importan más que el rendimiento máximo del entrenamiento.

Esta separación refleja la realidad de los sistemas de IA modernos, especialmente los modelos de combinación de expertos, modelos de razonamiento de contexto prolongado y cargas de trabajo de agentes que se mueven de manera irregular a través de la memoria, la red y los recursos informáticos.

Tendencias clave

Una tendencia importante es la creciente importancia de la topología. El rendimiento de la infraestructura de IA depende cada vez más de cómo se comunican los aceleradores dentro de un rack, entre módulos y entre grupos de memoria. Otra tendencia es el diseño de placas y silicio específico para cargas de trabajo.

Los clústeres de entrenamiento se benefician de un rendimiento agregado máximo y operaciones colectivas de alta velocidad, mientras que los clústeres de inferencia a menudo necesitan una latencia más baja, una mejor utilización en tamaños de lote variables y un consumo de energía predecible. Una tercera tendencia es el codiseño de software y hardware.

Funciones como motores de memoria especializados, aceleración colectiva y orquestación de datos se vuelven más valiosas cuando los compiladores y los marcos de servicio pueden exponerlos claramente a los desarrolladores de modelos.

Analisis de mercado

El mercado de aceleradores de IA ya no se define únicamente por las alternativas de GPU o las comparaciones de TOPS sin procesar. Los hiperescaladores, las empresas modelo y las plataformas de IA empresarial están evaluando el costo total de propiedad en relación con el precio del acelerador, las redes, la configuración de la memoria, la energía del rack, la refrigeración, la migración del software y la continuidad del suministro.

TPU v8 fortalece la estrategia interna de infraestructura de inteligencia artificial de Google y también indica al mercado de semiconductores en general que la eficiencia de la inferencia será un campo de batalla decisivo. A medida que la implementación del modelo escala más rápido que el entrenamiento de modelos de frontera, el hardware centrado en la inferencia puede convertirse en un problema de planificación de capacidad y abastecimiento mayor que el hardware de entrenamiento solo.

Implicaciones de abastecimiento

Para los equipos de adquisiciones, TPU v8 refuerza la necesidad de evaluar la lista de materiales completa del sistema. La selección de memoria, las interconexiones ópticas o eléctricas, los módulos de alimentación, los componentes de refrigeración, los sustratos, el empaquetado avanzado y la confiabilidad a nivel de placa afectan el riesgo de implementación.

Los clusters orientados a la capacitación y a la inferencia pueden requerir diferentes caminos de calificación, planificación de repuestos y modelos de riesgo de proveedores. Los equipos de EMS deben prepararse para configuraciones de servidores más especializados en lugar de una única plataforma genérica de acelerador de IA.

Recomendaciones

Los equipos de ingeniería y abastecimiento deben clasificar las necesidades de infraestructura de IA por tipo de carga de trabajo antes de seleccionar el hardware. La capacitación, el ajuste, la recuperación, la inferencia en tiempo real, la inferencia por lotes y la ejecución de agentes pueden tener diferentes cuellos de botella. Los equipos deben modelar la energía y la refrigeración con anticipación, verificar la disponibilidad de memoria e interconexión y comparar el TCO a nivel del sistema en lugar de solo el costo unitario del acelerador.

Al crear planes de capacidad a largo plazo, también es útil mantener alternativas calificadas para componentes de energía, térmicos, conectores, módulos ópticos y memoria porque estas categorías de soporte pueden convertirse en el factor limitante durante la expansión de la infraestructura de IA.

Cierre

Google TPU v8 muestra que la próxima etapa de la competencia de hardware de IA tiene que ver con una infraestructura equilibrada en lugar de solo con la computación máxima. Las plataformas ganadoras combinarán silicio, memoria, interconexión, software y ejecución de la cadena de suministro en sistemas que sean eficientes para la carga de trabajo exacta que atienden.

Para los equipos OEM y EMS, eso hace que la planificación temprana de la arquitectura y la estrategia de abastecimiento a nivel de componentes sean más importantes que nunca.